Knowledge Village, Dubai

Year IV - Semester I

2006–2007

Comprehensive examination (Closed Book)

Course No.: EEE UC 415

Course Title: DSP

Date: December 28, 2006

Time: 3 hours

Max. Marks = 40

#### (Clearly state any assumptions made)

1. Find the effect of coefficient quantisation on pole locations of the given second order IIR system, when it is realized in direct form I and in cascade form. Assume a word length of 4 bits through truncation.

$H(z) = 1/[(1 - 0.5 z^{-1})(1 - 0.45 z^{-1})]$

(5M)

- 2. Consider an audio band signal with a nominal band width of 4 KHz that has been sampled at a rate of 8 KHz. It is required to down rate the sampling frequency to 200 Hz. The highest frequency of interest after decimation is 75 Hz. Design a suitable optimum two stage decimator which will satisfy the following overall specifications.

- Pass band ripple = 0.01;

Stop band ripple = 0.0001

Filter length  $N = -10 \log (\delta_s \delta_p) - 13 + 1$ ;

14.6 Δf

where  $\Delta f$  is the normalized frequency.

Draw also the frequency response of the designed decimator stages.

(4M)

- 3. Starting with the equation for the mean square error, derive the Wiener Hopf equation to estimate the optimum weights of the adaptive filter.

- 4. A 4-point linear phase FIR filter is characterized by the following frequency samples. |H(k)| = 1, k = 0

$$= \frac{1}{2}$$

,  $k = 1$ , 3

= 0,  $k = 2$

- a) Determine the transfer function of the Recursive FIR frequency sampling filter and show that it contains four zeroes and three poles.

- b) Sketch the pole -zero diagram

- c) Determine the four coefficients of the filter which could be implemented. (bm)

- With a neat block diagram, explain the architecture of TMS 320 C5x

P-DSP.

(5M)

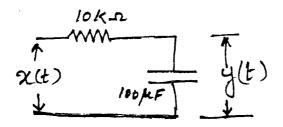

6. Using Bilinear – Z transform method of designing digital filters, determine the transfer function and hence the difference equation for the digital equivalent of the Resistance - Capacitance filter shown in figure below. Assume a sampling frequency of 150 Hz and a cut off frequency of 30 Hz.

(6M)

7. Obtain the coefficients of an FIR low pass digital filter to meet the specifications given below using window method.

Pass-band edge frequency: 3.4 KHz;

Stop band attenuation: 50 dB

Transition width: 0.6 KHz Sampling frequency: 8 KHz

Give your comments on the window used and the reason for your choice. (You may refer the windows table provided) (7 m)

Knowledge Village, Dubai Year IV – Semester I 2006–2007 Test I (Closed Book)

Course No.: EEE UC 415

Course Title: DSP

Date: November 02, 2006

Time: 50 Minutes

Max. Marks = 30

(6)

#### (Answer all Questions)

- 1. A discrete time filter transfer function is given by  $H(z) = (1 1.6 z^{-1} + z^{-2}) / (1 1.5 z^{-1} + 0.8 z^{-2})$

- a) What is its DC amplitude response?

- b) For the system transfer function given above, What are the radii of the poles and zeroes? (2+4)

- Obtain the digital filter transfer function of the analog filter with H(s) = (s+1) / (2s² + 5s + 2), using Impulse Invariant method. Assume a sampling frequency of 1kHz.

- An FIR digital filter has impulse response h(n) defined over the interval

0 ≤ n ≤ N-1. if N = 5 and h (n) satisfies the symmetry condition

h (n) = h (N-n-1), Show that the filter has a linear phase characteristics.

- Describe the various addressing modes of Programmable DSP TMS 320 C5X

- 5. Design a digital butterworth filter satisfying the constraints

$$0.707 \le |H(e^{j\omega})| \le 1 \text{ for } 0 \le \omega \le \pi/2$$

$|H(e^{j\omega})| \le 0.2 \text{ for } \sqrt[3]{4} \pi \le \omega \le \pi$

with T = 1 sec using bilinear transformation. Realise the filter using most convenient realization form. (6)

\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Knowledge Village, Dubai Year IV – Semester I 2006–2007 Test II (Open Book)

Course No.: EEE UC 415

Course Title: DSP

Date: 07<sup>th</sup> December, 2006

Time: 50 min

Max. Marks = 30

( State clearly the assumptions made if any )

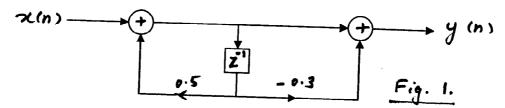

1. Scale the first order digital filter structure of figure 1 using  $\mathcal{L}_2$  – norm scaling rule (8)

2. Design an efficient decimator for reduction in sampling rate of a signal from 12 kHz to 400 Hz. The highest frequency of interest of the signal is 180 Hz. Assume that an optimum linear phase FIR filter is to be used, with an overall pass band ripple of 0.01 and stop band deviation of 0.002. (Consider all possible no. of stages and decimation factors).

Also draw the block diagram and the frequency response of each stage.

(12)

3. Show that the impulse response of an ideal band pass filter is given by  $h_D(n) = \frac{\sin(n\omega_2)}{n\Pi} - \frac{\sin(n\omega_1)}{n\Pi} \quad \text{for } n \neq 0$   $= 2(f_2 - f_1) \quad \text{for } n = 0$ (8)

Knowledge Village, Dubai Year IV – Semester I 2006–2007 Quiz I (Open Book)

| Course No.: EEE UC 415                                                                                                                    | Course Title: DSP                                                                             |                                                         |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| Date: October 16, 2006                                                                                                                    | Time: 30 Minutes                                                                              |                                                         |  |

| (Question nos. 1-20 carries one m                                                                                                         | nark each and Question Nos 21-                                                                | 30 carries 2 marks each )                               |  |

|                                                                                                                                           | PART A                                                                                        | ······································                  |  |

| In modified Harward Archite separate bus is used for memory.                                                                              | ecture, for fetching the content ofmemory                                                     | program and data memory, a and a single bus is used for |  |

| VLIW architecture differs fro     a) Instruction Cache b)     c) Use pipelining d)                                                        | m conventional P-DSP in which<br>Number of functional Units<br>A single word fetch from memor |                                                         |  |

| <ul><li>3. The addressing mode that is co</li><li>a) indirect addressing</li><li>c) Bit reversed addressing</li><li>d) indirect</li></ul> | onvenient for FFT computation is<br>b) circular mode<br>Memory mapped                         | 5                                                       |  |

| 4. The holds a) Preg, 32 b) Treg, 32 c) A                                                                                                 | the result of multiplication and is<br>Acc, 32 d) Preg, 16                                    | s bit wide                                              |  |

| 5 permitthey are either fed to ALU or st                                                                                                  | its the contents of memory to be stored to memory.                                            | shifted by 0-16 bits before                             |  |

| 6. The bit of ST1 used for compara a) SXM b) OV c) To                                                                                     | ing one register against and the                                                              |                                                         |  |

| a) SXM b) OV c) To                                                                                                                        | C d) C                                                                                        | egister memory is                                       |  |

| 7. The pointers that are contained in a) ARP b) DP c) All                                                                                 | in the status register0 are  RB d) INTM e) IPTE                                               | <u> </u>                                                |  |

| 8. The data memory used with C52 ———— words long.                                                                                         | •                                                                                             |                                                         |  |

| 9. The memory mapped direct addr                                                                                                          | essing mode is used to access da                                                              | ta in page                                              |  |

| a) 1 b) 0 c) 511                                                                                                                          |                                                                                               | to.                                                     |  |

| 10. Using<br>execu       | g RPT #k instruction uted is                 | n, the maximum                          | no. of times a s   | ingle instruction ca                        | n be repeatedly  |

|--------------------------|----------------------------------------------|-----------------------------------------|--------------------|---------------------------------------------|------------------|

| 11. What                 | addressing mode is                           | represented by the                      | he syntax *0+      |                                             |                  |

| 12. What                 | is the syntax for lon                        | g immediate add                         | ressing? Give a    | an example?                                 |                  |

| 13. The tw               | o special purpose me                         | emory mapped re                         | egisters in the (  | CPU are                                     | and              |

| 14. Name ti              | he memory mapped                             | registers that cor                      | ntrol the circula  | r buffer operation.                         |                  |

| 15. The                  | bit                                          | register (                              | enables and dis    | ables the circular b                        | affer operation. |

| 16. In the dir specified | ect addressing mode<br>in the instruction an | e of C5X                                | bits are t         | bits of the addr<br>aken from the DP        | ess is           |

|                          | nory – mapped regis<br>ta page pointer valu  |                                         | ie MMRs can i      |                                             |                  |

| 8. The starting will be  | ng address of the dat                        | a memory page p                         | oointed by the I   | OP register whose c                         | ontent is 7      |

| 9. When MA               | CD instruction is exe                        | ecuted, the produ                       | ict register is sl | nifted by the count                         | specified by     |

| For all the r            | nultiplication instruction and the other     | ctions of C5X, or<br>r can be specified | ne of the operar   | nds is to be kept in<br>of the addressing m | odes.            |

|                          |                                              |                                         |                    |                                             |                  |

Knowledge Village, Dubai Year IV - Semester I 2006-2007 Test I (Closed Book)

Course No.: EEE UC 415

Course Title: DSP

Date: November 02, 2006

Time: 50 Minutes

Max. Marks = 30

(Answer all Questions)

- A discrete time filter transfer function is given by H(z) =  $(1 - 1.6 z^{-1} + z^{-2})/(1 - 1.5 z^{-1} + 0.8 z^{-2})$

- a) What is its DC amplitude response?

- b) For the system transfer function given above, What are the radii of the (2+4)

- Obtain the digital filter transfer function of the analog filter with  $H(s) = (s+1)/(2s^2 + 5s + 2)$ , using Impulse Invariant method. Assume a sampling frequency of 1kHz. (6)

- An FIR digital filter has impulse response h(n) defined over the interval  $0 \le n \le N-1$ . if N = 5 and h (n) satisfies the symmetry condition h (n) = h (N-n-1), Show that the filter has a linear phase characteristics.

- Describe the various addressing modes of Programmable DSP TMS 320

- Design a digital butterworth filter satisfying the constraints 5.

$$0.707 \le |H(e^{j\omega})| \le 1$$

for  $0 \le \omega \le \pi/2$

$$|H(e^{j\omega})| \le 0.2 \text{ for } \sqrt[3]{\pi} \le \omega \le \pi$$

with T = 1 sec using bilinear transformation. Realise the filter using most (6)