### Knowledge Village

III-Year - 1<sup>st</sup> SEMESTER 2003-2004 Microelectronic Circuits (EEE UC424/INSTR UC313) Comprehensive Exam (Closed Book)

Date: 11/1/2004 Time: 3 Hours Max Mark: 80

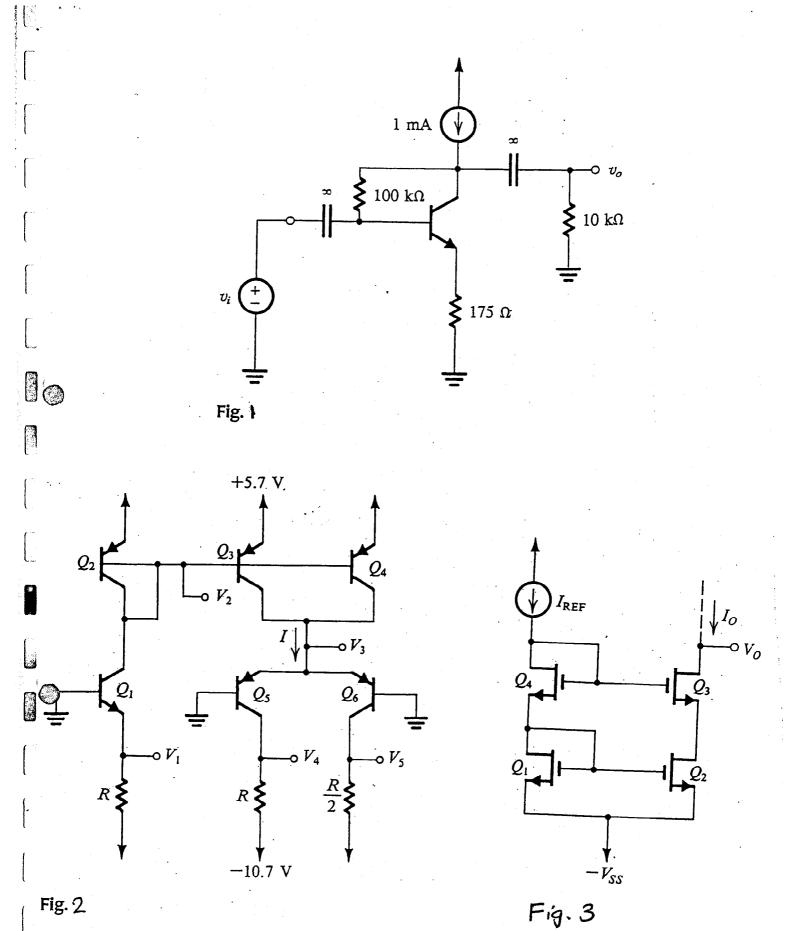

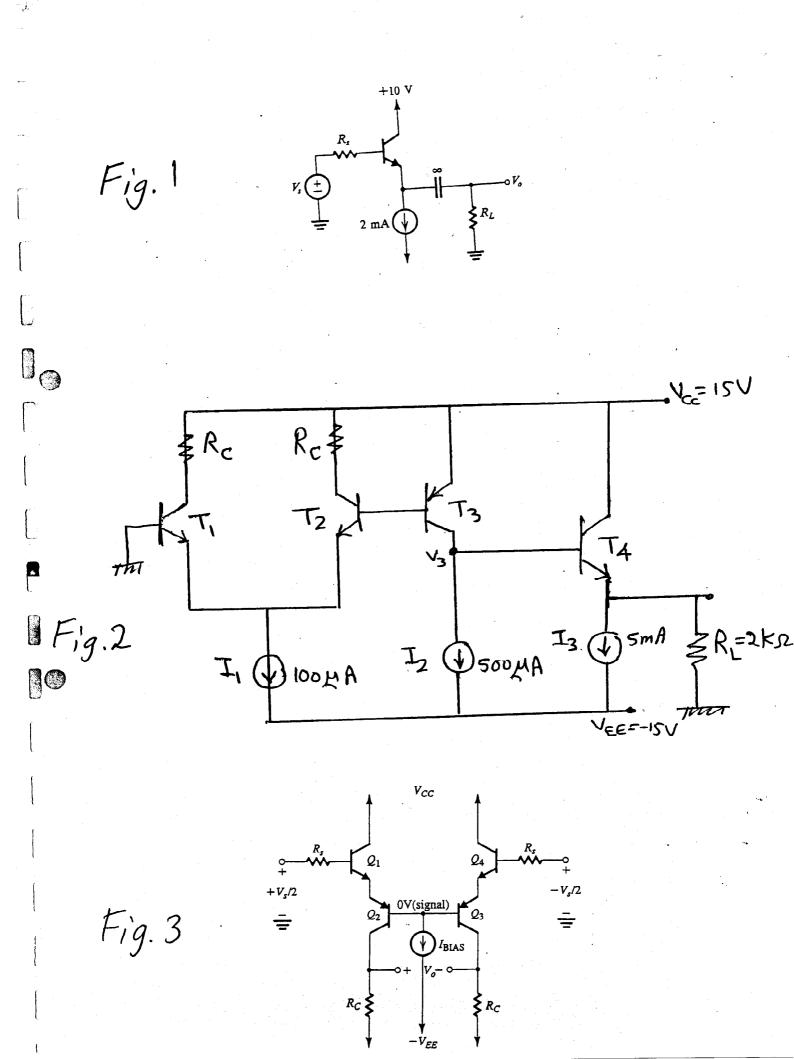

**Q**1}

The BJT in the circuit of Fig. 1 has  $\beta=100$ .

- a) Find the dc collector current and the dc voltage at the collector.

- b) Draw the small-signal equivalent circuit of the amplifier using the T-model. Analyze the resulting circuit to determine the voltage gain  $v_0/v_i$ .

[10 M]

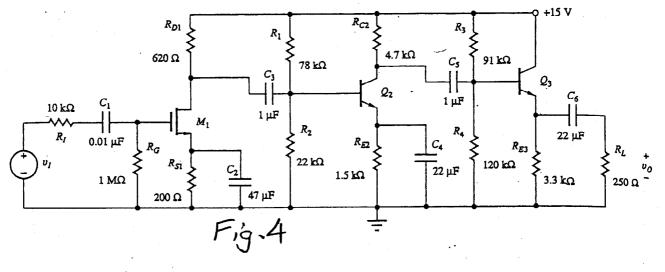

**Q2**}

For the circuit in Fig.2 let  $|V_{BE}|=0.7$  V and  $\beta=\infty$ . Find I,  $V_1$ ,  $V_2$ ,  $V_3$ ,  $V_4$ , and  $V_5$ ,

for a)  $R = 10 \text{ k}\Omega$

b)  $R = 100 k\Omega$

[10 M]

**Q**3}

In the cascaded mirror circuit shown in Fig.3 all transistors has  $V_t=1V$ ,  $\mu_n$   $C_{ox}=40~\mu\text{A/V}^2$ , L=5  $\mu\text{m}$ , and  $V_A=30V$ . Widths  $W_1=W_4=10\mu\text{m}$ , and  $W_2=W_3=200\mu\text{m}$ . The reference current is  $10\mu\text{A}$  and  $V_{ss}=0$  V.

- a) What output current results?

- b) What are the voltages at the gates of  $Q_2$  and  $Q_3$ ?

- c) What is the lowest voltage at the output for which the current-source operation is possible?

- d) What are the values of  $g_m$  and  $r_o$  of  $Q_2$  and  $Q_3$ ?

- e) What is the input and output resistance of the mirror?

[12 M]

**Q4**}

The three stage amplifier circuit in Fig.4 has the following data:

|                | Q-point       | g <sub>m</sub> (mS) | $r_{\pi}(k\Omega)$ | $r_{o}(k\Omega)$ | β   | $C_{gs}$ , $C_{\pi}$ | $C_{gd}$ , $C_{\mu}$ | $r_{x}(\Omega)$ |

|----------------|---------------|---------------------|--------------------|------------------|-----|----------------------|----------------------|-----------------|

| $M_1$          | 5mA, 10.9 V   | 10                  | ∞                  | 12.2             | ∞   | 5 pF                 | 1 pF                 | 0               |

| $Q_2$          | 1.67mA, 5.09V | 62.8                | 2.39               | 54.2             | 150 | 39 pF                | 1 pF                 | 250             |

| Q <sub>3</sub> | 1.99mA, 8.36V | 79.6                | 1.0                | 34.4             | 80  | 50 pF                | 1 pF                 | 250             |

Use the open circuit time-constant (OCTC) and the short-circuit time constant (SCTC) techniques to estimate the upper- and lower- cutoff frequencies and the bandwidth for the given amplifier. [14 M]

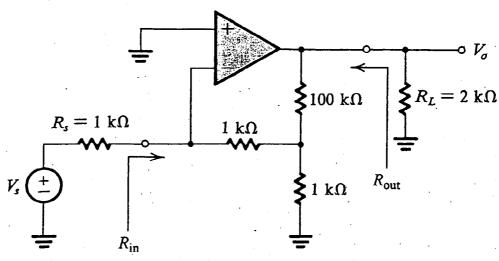

**Q5**}

For the shunt-shunt feedback circuit in Fig.5, find the voltage gain  $V_o/V_s$ , the input resistance  $R_{in}$ , and output resistance using the feedback method. The op amp has open-loop gain  $\mu$ =10<sup>4</sup> V/V,  $R_{id}$ =100 k $\Omega$  and  $r_o$  = 1 k $\Omega$ .

[12 M]

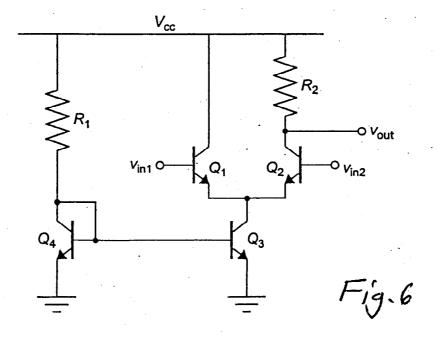

**Q6**}

The circuit in Fig. 6 has the following element values:  $V_{CC}$ =5V,  $R_L$ =3.3 k $\Omega$ ,  $R_2$ =2.2 k $\Omega$ . For all transistors,  $\beta$ =  $\infty$ ,  $V_A$ =20V.

- a) Compute the collector currents of  $Q_1$ ,  $Q_2$  and  $Q_3$  and the collector voltage of  $Q_3$ .

- b) Compare the maximum and minimum common-mode voltage such that  $Q_1$ ,  $Q_2$ , and  $Q_3$  are biased in the forward-active region.

- c) Compute the differential-to-single-ended gain.

- d) Compute the common-mode voltage gain and the CMMR. [10 M]

**Q7**}

- A) Design a class B power amplifier that will deliver an average power of 20W to an 8Ω load. Assume that the supply voltage is larger than the peak voltage by 5V. Determine the power conversion efficiency. Also find the maximum power that each transistor can dissipate safely.

- B) A power transistor is specified to have a maximum junction temperature of  $130^{\circ}$ C. When operating at this junction temperature with a heat sink, the case temperature is found to be  $90^{\circ}$ C. The case is attached to the heat sink with a bond having a thermal resistance  $\theta_{CS} = 0.5$  °C/W and the thermal resistance of the heat sink  $\theta_{SA} = 0.1$  °C/W. If the ambient temperature is  $30^{\circ}$ C what is the power being dissipated in the device? What is the thermal resistance of the device  $\theta_{JC}$ , from junction to case.

[12 M]

Fig. 5

## Knowledge Village

III-Year - 1<sup>st</sup> SEMESTER 2003-2004 Microelectronic Circuits (EEE UC424/INSTR UC313) Test-I (Closed Book)

Date: 2/11/2003 Time: 50 Min Max Mark: 50

**Q1**}

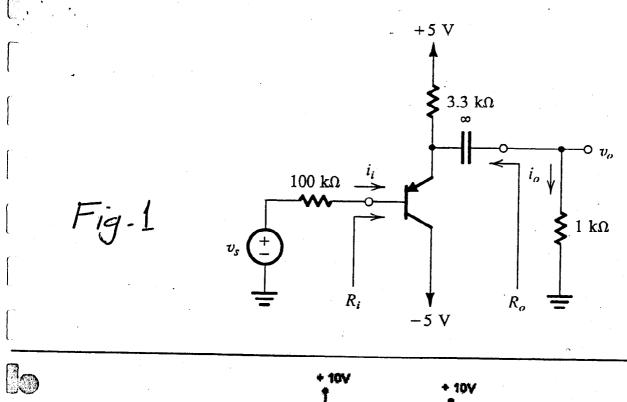

For the circuit shown in Fig.1 find the dc emitter current. Assume that  $\beta=120$ . Neglecting  $r_o$ , find the input resistance  $R_i$ , the voltage gain  $v_o/v_s$ , the current gain  $i_o/i_i$ , and the output resistance  $R_o$ .

**Q2**}

[12]

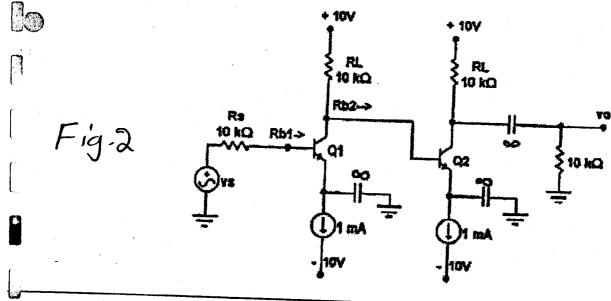

In the circuit shown in Fig. 2 and for  $\beta=150$ , find  $v_o/v_{b2}$ ,  $R_{b2}$ ,  $v_{b2}/v_{b1}$ ,  $R_{b1}$ ,  $v_{b1}/v_{s}$ ,  $v_o/v_{s}$ . [12]

**Q3**}

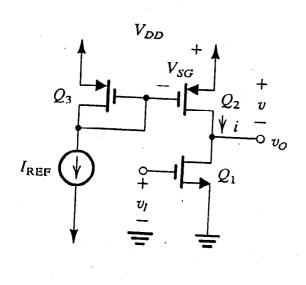

For the CMOS amplifier circuit shown in Fig.3,  $k_n=2.5k_p=50~\mu\text{A/V}^2$ ,  $|V_t|=1v$ , and  $|V_A|=50V$ . Find  $I_{IREF}$  and (W/L) to obtain a voltage gain of -100V/V and an output resistance of  $1M\Omega$ .

**Q4**}

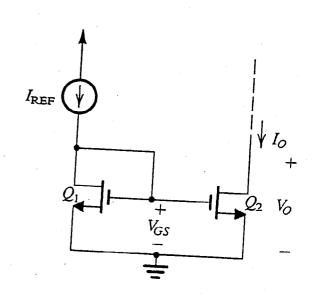

C onsider the circuit shown in Fig.4, find the ratio  $I_{\bullet}/I_{REF}$  for each of the following cases:

- a.  $L_1=L_2$ ,  $W_2=3W_1$

- b.  $L_1=L_2$ ,  $W_2=10W_1$

- c.  $L_1 = L_2$ ,  $W_2 = W_{1/2}$

- d.  $W_2=W_1, L_1=2L_2$

- e.  $W_2=W_1$ ,  $L_1=10L_2$

- f.  $W_2=W_1, L_1=L_2/2$

- g.  $W_2=3W_1$ ,  $L_1=3L_2$

Fig.3

Fig.4

# BITS Pilani Dubai Yr, 1st semester Micro Electronic Circuits (EEE UC 424/EEE U(313) OPEN BOOK

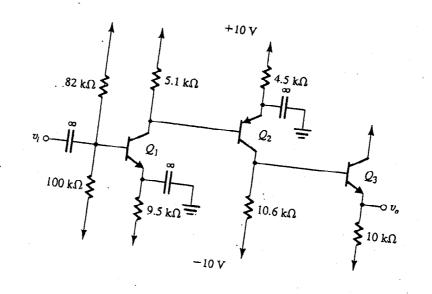

Figure P6.121 shows a three-stage amplifier in which the stages are directly coupled. The amplifier, however, utilizes bypass capacitors, and, as such, its frequency response falls off at low frequencies. For our purposes here, we shall assume that the capacitors are sufficiently large to act as perfect short circuits at all signal frequencies of interest.

- (a) Find the dc bias current in each of the three transistors. Also find the dc voltage at the output. Assume  $|V_{BE}| = 0.7 \text{ V}$ ,  $\beta = 100$ , and neglect the Early effect.

- (b) Find the input resistance and the output

- (c) Use the current-gain method to evaluate the

Opiz solution

Micro Electronic Ci EEE UC 424

at Ic~ ImA.

(b)

$$R_{in} = 82 //100 //\Gamma_{mi}$$

where  $\Gamma_{mi} = \frac{\beta}{g_{mi}} = \frac{100}{40} = 2.5 \text{ kg}$

$R_{in} = 82 //100 //2.5 = 2.37 \text{ kg}$

$R_{out} = 10 \text{ kg} // [\Gamma_{e3} + \frac{10.6 \text{ kg}}{\beta+1}]$

$= 10 // [0.025 + \frac{10.6}{101}]$

$= 128 \Omega$

(c)  $\frac{1}{V_{i}} = \frac{9}{m_{i}} = 40 \text{ mA/V}$

$\frac{1}{V_{i}} = \frac{5.1}{5.1 + \Gamma_{m2}} = \frac{5.1}{5.1 + 2.5} = 0.671 \text{ A/A}$

$\frac{1}{V_{i2}} = \frac{5.1}{5.1 + \Gamma_{m2}} = \frac{5.1}{5.1 + 2.5} = 0.671 \text{ A/A}$

$\frac{1}{V_{i2}} = \beta_{2} = 100 \text{ A/A}$

$\frac{1}{V_{i3}} = \beta_{2} = 100 \text{ A/A}$

$\frac{1}{V_{i3}} = \frac{10.6}{10.6 + (\beta+1)(r_{e3}+10)} = 0.01036 \text{ A/A}$

$\frac{1}{V_{i3}} = \beta_{3}+1=101$

$V_{ij} = \frac{10}{V_{ij}} = \frac{10}{$

## BITS, PILANI - DUBAI CAMPUS Knowledge Village

III-Year - 1st SEMESTER 2003-2004 Microelectronic Circuits (EEE UC424/INSTR UC313) Test-II (Open Book)

Date:14/12/2003 Time: 50 Min Max Mark: 40

**Q**1}

For the circuit shown in Fig.1, find the midband gain, the frequency of high-frequency dominant pole, and estimate of f<sub>H</sub> using the method of open-circuit time constants, and the frequency of the transfer function zero. Given that  $\beta=100$ ,  $f_T=400MHz$ ,  $C_\mu=2pF$ , (14 Marks)  $R_L=R_s=1k\Omega$ .

**Q2**}

Find the differential mode voltage gain, CMMR, input resistance and output resistance for the amplifier shown in Fig.2, if  $\beta_1$ =  $\beta_2$ =  $\beta_3$ =  $\beta_4$ =100,  $V_A$ =89V. Assume the internal (14 Mark) resistance for the current source is  $750k\Omega$ .

**Q3**}

For the circuit shown in Fig.3 all transistors are matched having  $\beta$ =150, f<sub>T</sub>=1GHz and C<sub>μ</sub>=0.3 pF. Each transistor operates at 150μA emitter current. The collector load resistors are  $2.7k\Omega$ . The source resistances are each  $10k\Omega$ . Find the midband gain and the upper 3dB (12 Marks) frequency.

Knowledge Village

III-Year - 1<sup>st</sup> SEMESTER 2003-2004 Microelectronic Circuits (EEE UC424/INSTR UC313)

Quiz-II

\_

$\mathbf{A}$

Date: 24/12/2003 Time: 25 Min

Max Mark: 10

A scries-shunt feedback amplifier, has an A circuit for which A = 100 V/V,  $R_i = 10 \text{ k}\Omega$  and  $R_o = 10 \Omega$ , and a  $\beta$  circuit with  $\beta = 0.1 \text{ V/V}$ ,  $R_1 = 2 \text{ k}\Omega$  and  $R_2 = 18 \text{ k}\Omega$ . When operating from a zero-impedance source and with no load, what is the overall gain and input and output resistances that result with feedback? If this feedback amplifier is connected between a 0.1 V rms source whose resistance is 10 k $\Omega$  and a load of 100  $\Omega$ , what does the output voltage become?

Knowledge Village

III-Year - 1st SEMESTER 2003-2004

Microelectronic Circuits (EEE UC424/INSTR UC313)

Quiz-II

B

Date: 24/12/2003

Time: 25 Min

Max Mark: 10

A feedback amplifier connected in the series-series topology uses a basic amplifier having a gain of 900 V/V, an input resistance of 20 k $\Omega$  and an output resistance of 1 k $\Omega$ , with a feedback network for which  $\beta$  = 50 V/A,  $R_{11}$  = 10 k $\Omega$  and  $R_{22}$  = 200 $\Omega$ . The amplifier operates between a 10 k $\Omega$  source and a 1 k $\Omega$  load. Find A,  $A_f$  as well as the resistance  $R_{in}$  and  $R_{out}$  seen by the source and the load.